# 16-bit Proprietary Microcontroller

**CMOS**

# F<sup>2</sup>MC-16L MB90650A Series

# MB90652A/653A/P653A/654A/F654A

#### ■ DESCRIPTION

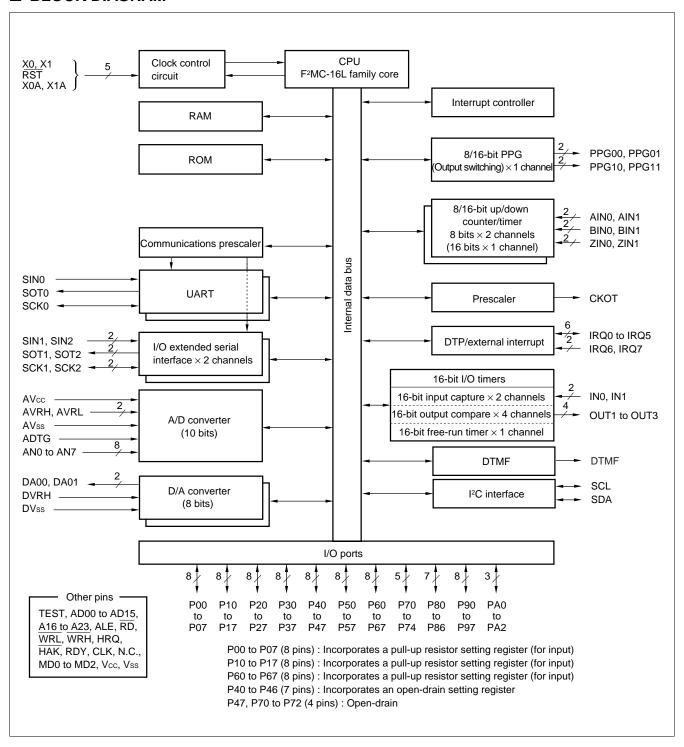

The MB90650A series are 16-bit microcontrollers designed for high speed real-time processing in consumer product applications such as controlling celluar phones, CD-ROMs, or VTRs. Based on the F<sup>2</sup>MC<sup>\*1</sup>-16L CPU core, an F<sup>2</sup>MC-16L is used as the CPU. This CPU includes high-level language-support instructions and robust task switching instructions, and additional addressing modes. In order to reduce the consumption current, dual-clock (main/sub) is used. Furthermore, low consumption power supply is achieved by using stop mode, sleep mode, watch mode, pseudo-watch mode, CPU intermittent operation mode.

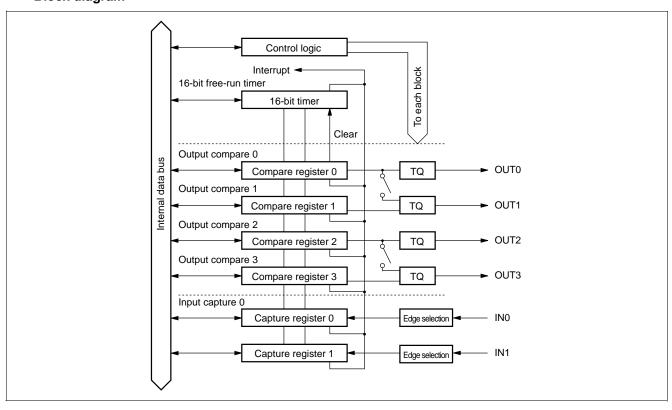

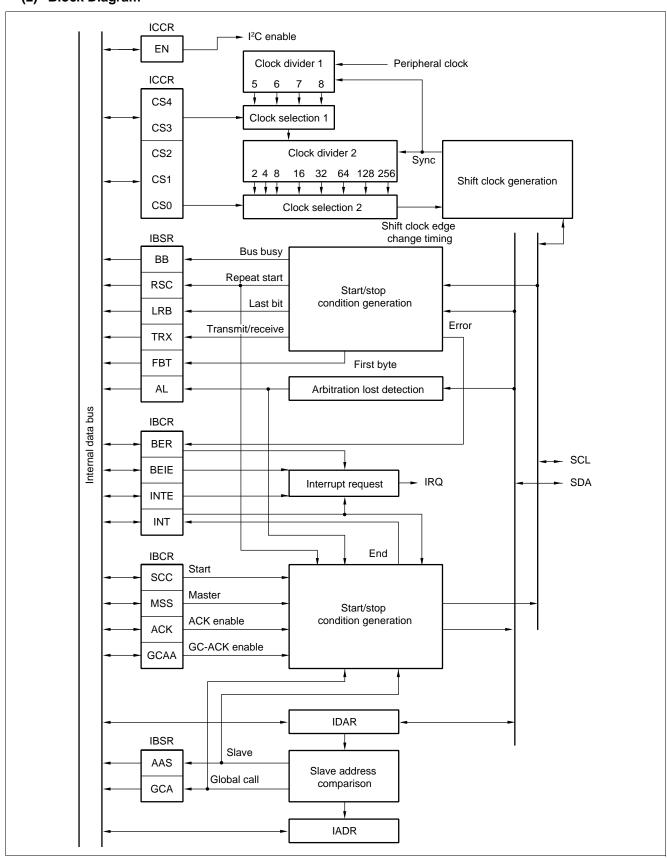

Microcontrollers in this series have built-in peripheral resources including 10-bit A/D converter, 8-bit D/A converter, UART, 8/16-bit PPG, 8/16-bit up/down counter/timer, I<sup>2</sup>C interface<sup>-2</sup>, 8/16-bit I/O timer (input capture, output compare, and 16-bit free-run timer).

- \*1:F2MC stands for FUJITSU Flexible Microcontroller.

- \*2:Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

### **■ FEATURES**

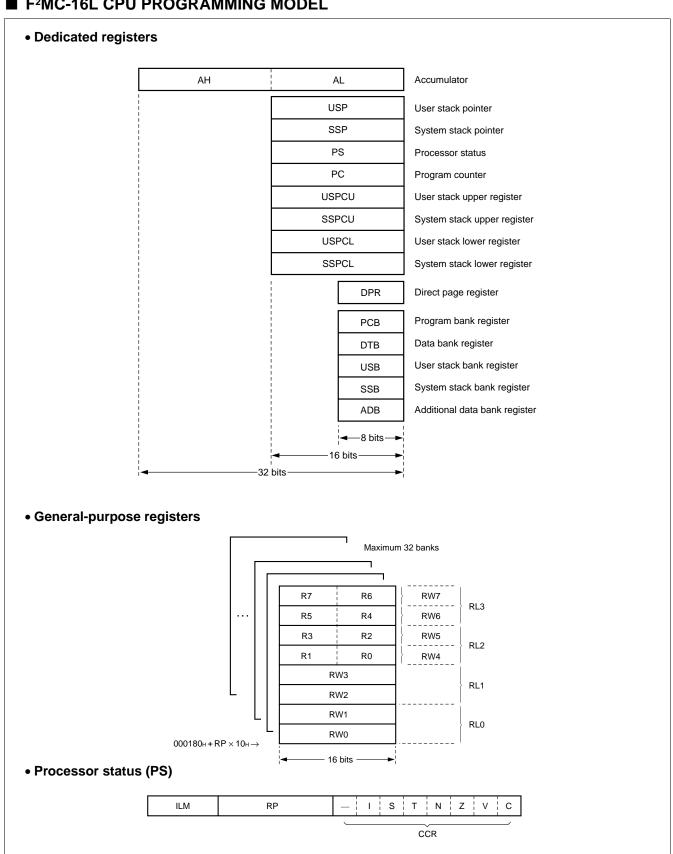

#### F<sup>2</sup>MC-16L CPU

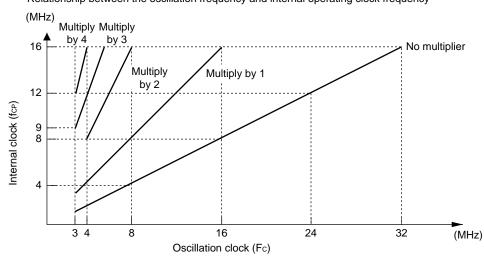

- Minimum execution time: 62.5 ns/4 MHz oscillation (Uses PLL clock multiplication) maximum multiplier = 4

- Instruction set optimized for controller applications

Object code compatibility with F<sup>2</sup>MC-16(H)

(Continued)

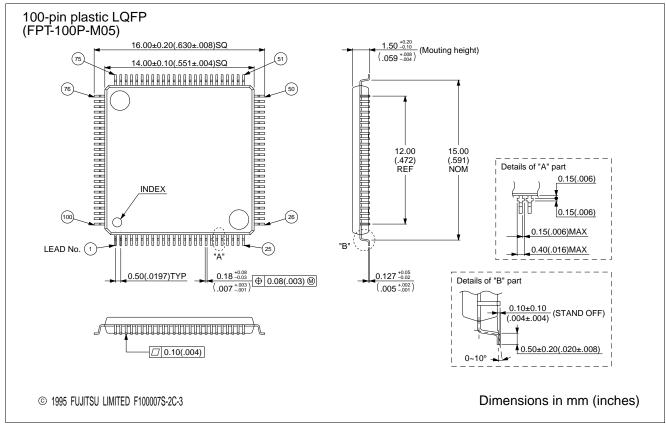

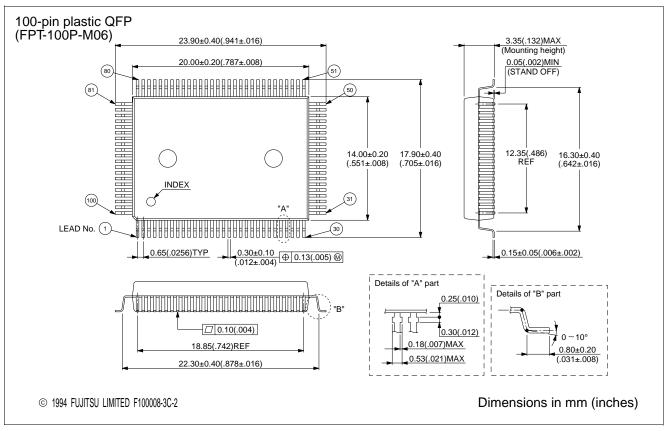

## **■ PACKAGE**

## (Continued)

Wide range of data types (bit, byte, word, and long word) Improved instruction cycles provide increased speed

Additional addressing modes: 23 modes

High code efficiency

Access methods (bank access, linear pointer)

High precision operations are enhanced by use of a 32-bit accumulator Extended intelligent I/O service (access area extended to 64 Kbytes)

Maximum memory space: 16 Mbytes

• Enhanced high level language (C) and multitasking support instructions Use of a system stack pointer

Enhanced pointer indirect instructions

Barrel shift instructions

- Improved execution speed: Four byte instruction queue

- Powerful interrupt function

- Automatic data transfer function that does not use instruction (extended I<sup>2</sup>OS)

## **■ PRODUCT LINEUP**

| Part number                    |                                                                                                       |                                                                                                               |                                                                             |                                                                                              |                                                                                                |                |

|--------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------|

|                                | MB90652A                                                                                              | MB90653A                                                                                                      | MB90P653A                                                                   | MB90V650A                                                                                    | MB90654A                                                                                       | MB90F654A      |

| Item                           |                                                                                                       |                                                                                                               |                                                                             |                                                                                              | M 1 DOM                                                                                        |                |

| Classification                 | Mask RC                                                                                               | OM product                                                                                                    | OTPROM product                                                              | For evaluation                                                                               | Mask ROM<br>product                                                                            | FLASH product  |

| ROM size                       | 64 Kbytes                                                                                             | 128                                                                                                           | Kbytes                                                                      | _                                                                                            | 256 H                                                                                          | Kbytes         |

| RAM size                       | 3 Kbytes                                                                                              |                                                                                                               | 5 Kbytes                                                                    |                                                                                              | 8 KI                                                                                           | bytes          |

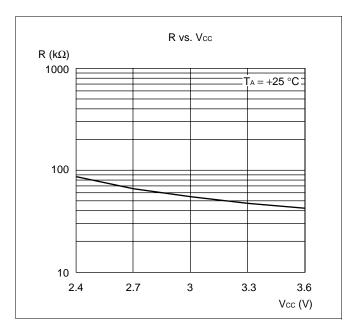

| Power supply voltage           | 2.2 V                                                                                                 | to 3.6 V                                                                                                      | 2.7 V to                                                                    | 5.5 V                                                                                        | 2.2 V to 3.6 V                                                                                 | 2.4 V to 3.6 V |

| CPU functions                  | Instructi<br>Instructi<br>Data bit<br>Minimur                                                         | nber of instructio<br>on bit length:<br>on length:<br>length:<br>n execution time:<br>t processing time       | :                                                                           | 340<br>8/16 bits<br>1 to 7 bytes<br>1/4/8/16/32 bits<br>62.5 ns/4 MHz (P<br>1.0 μs/16 MHz (n |                                                                                                |                |

| Ports                          |                                                                                                       | s (N-channel ope<br>s (CMOS):                                                                                 | ·                                                                           | 4<br>75 (Input pull-up<br>Can be set a<br>79                                                 | resistors available<br>s N-channel oper                                                        |                |

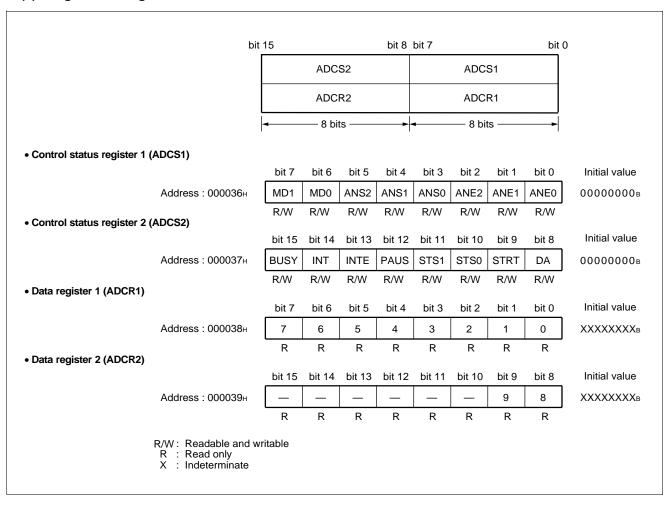

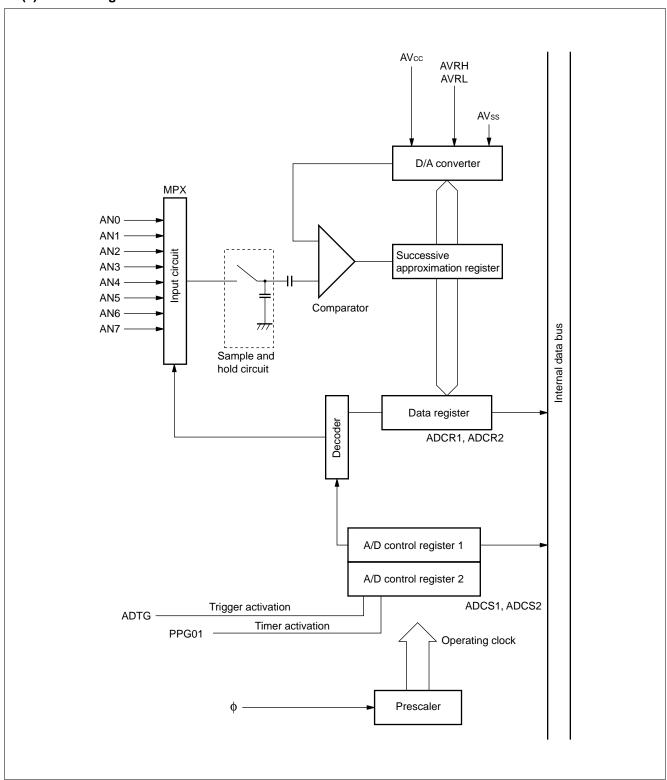

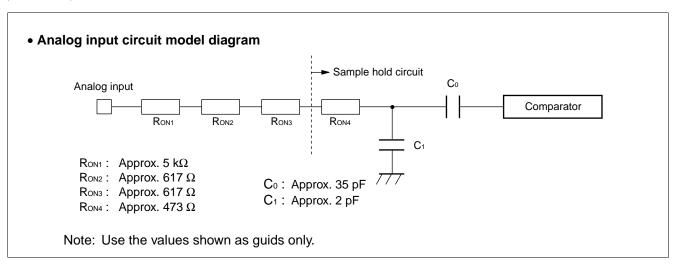

| A/D converter                  | Analog inputs : 8 channels<br>10-bit resolution<br>Conversion time : minimum<br>6.13 µs/16 MHz        |                                                                                                               | Analog inputs<br>10-bit res<br>Conversion time :<br>μs/8 Ν                  | solution<br>minimum 12.25                                                                    | Analog inputs : 8 channels<br>10-bit resolution<br>Conversion time : minimum<br>6.13 µs/16 MHz |                |

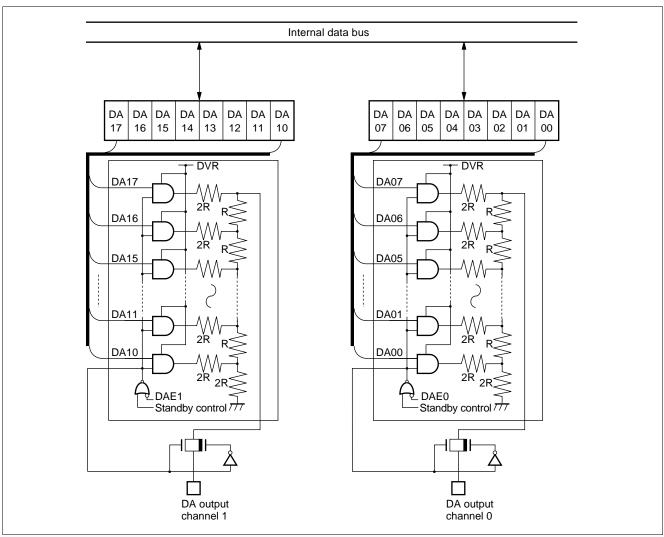

| D/A converter                  |                                                                                                       |                                                                                                               |                                                                             | independent),<br>on, R-2R type                                                               |                                                                                                |                |

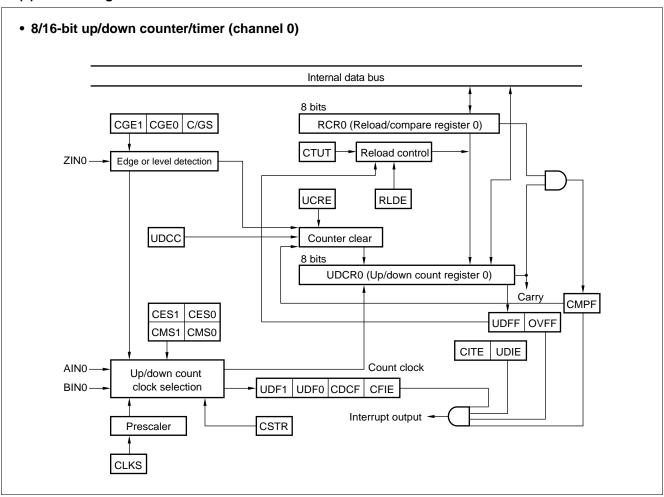

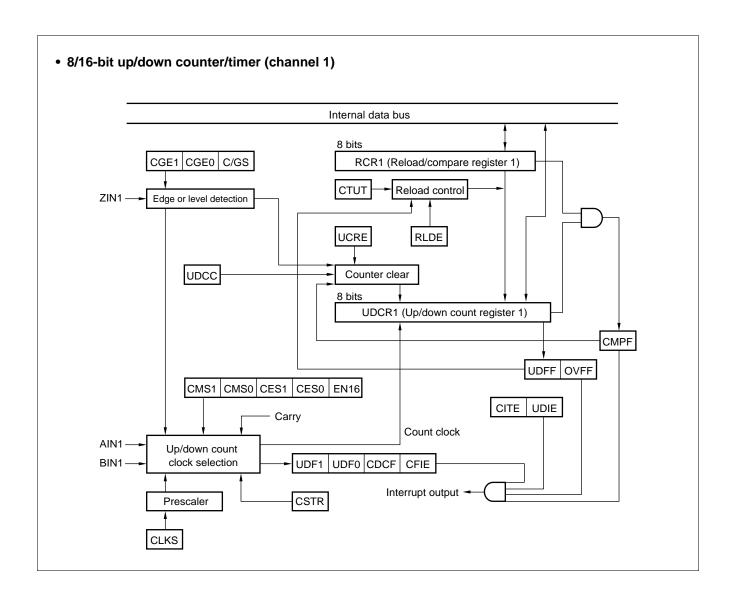

| 8/16-bit up/down counter/timer |                                                                                                       | 16 b                                                                                                          | oits × 1 channel/8 bit<br>Includes reload and                               |                                                                                              |                                                                                                |                |

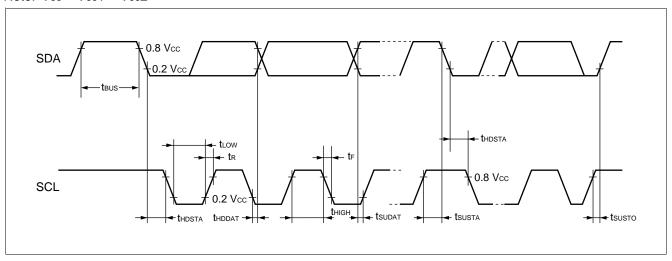

| I <sup>2</sup> C interface     |                                                                                                       |                                                                                                               |                                                                             | iannel<br>ive mode available                                                                 | е                                                                                              |                |

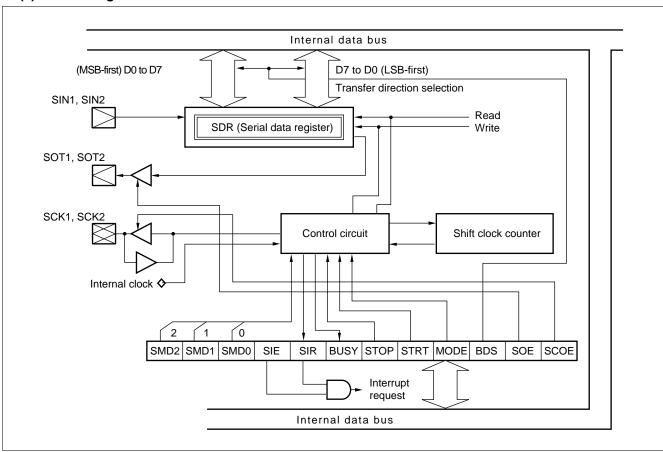

| UART                           |                                                                                                       |                                                                                                               | Clock synchrono                                                             | nannel<br>ous communication<br>ous communication                                             | n<br>on                                                                                        |                |

| I/O extended serial interface  |                                                                                                       |                                                                                                               | 8 bits × 2<br>LSB-first or MSB-firs                                         | 2 channels<br>st operation selec                                                             | able                                                                                           |                |

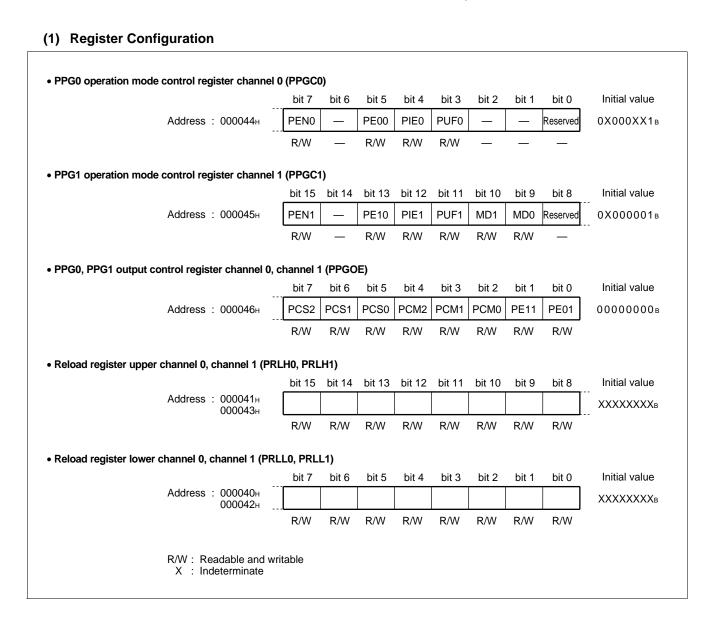

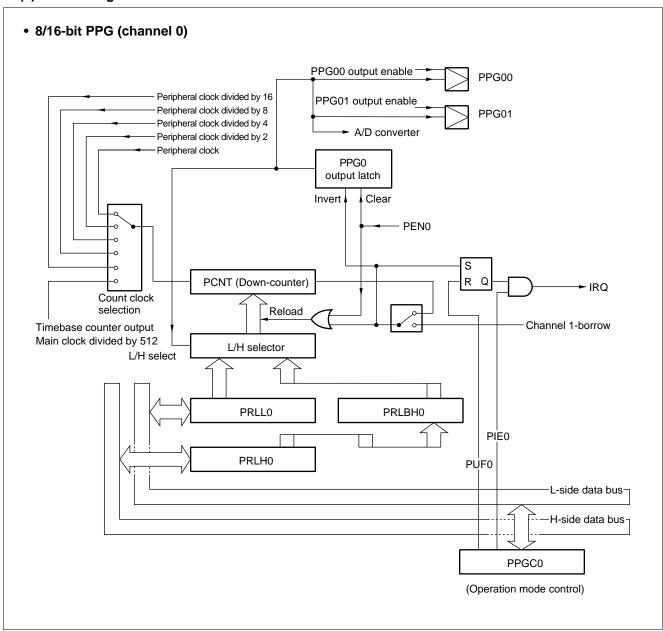

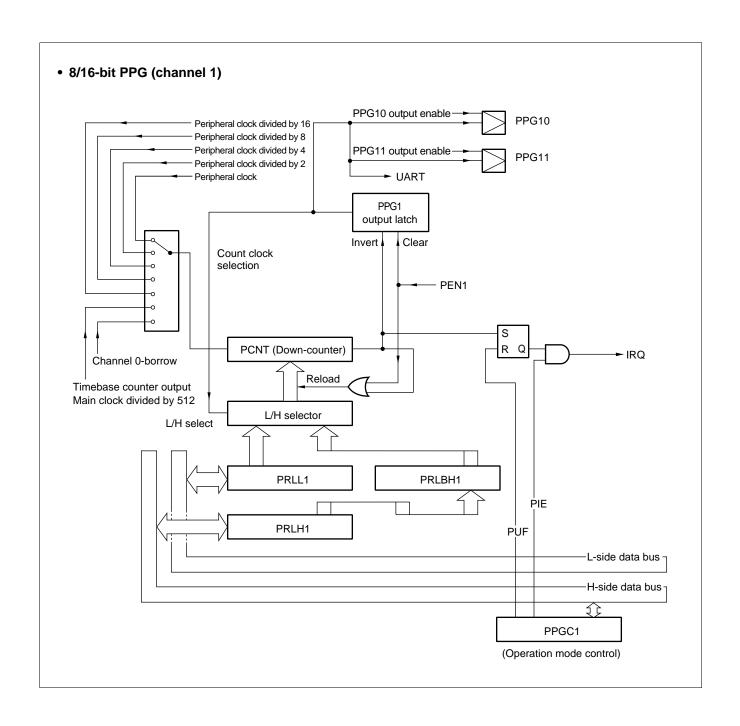

| 8/16-bit PPG                   |                                                                                                       | 8 bit                                                                                                         | $ts \times 2$ channels/16 b                                                 | its $\times$ 1 channel se                                                                    | electable                                                                                      |                |

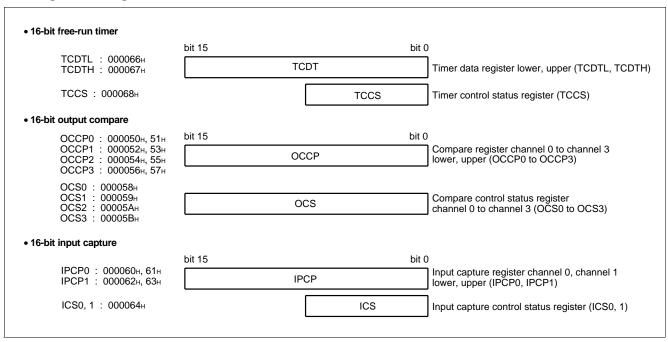

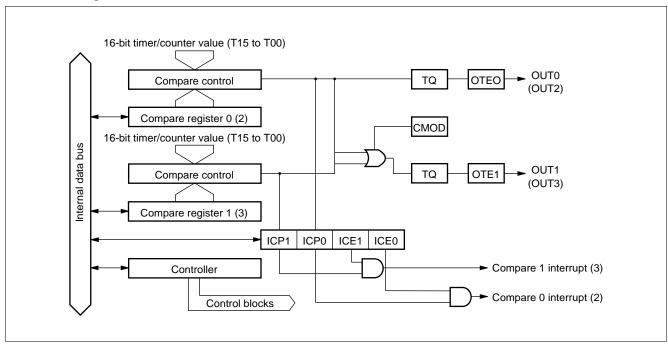

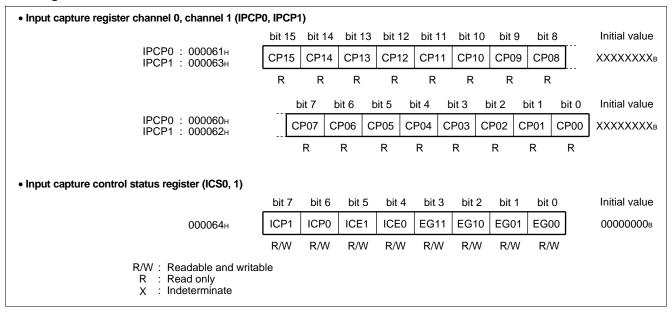

| 16-bit I/O timer               | (Input ca                                                                                             | apture × 2 chann                                                                                              | 1 ch<br>els, output compare                                                 | ex 4 channels, an                                                                            | d free-run timer ×                                                                             | 1 channel)     |

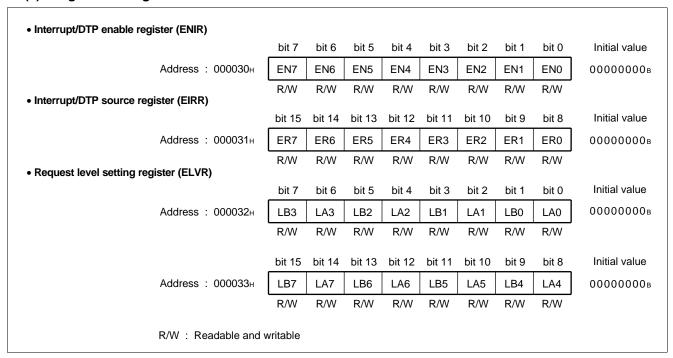

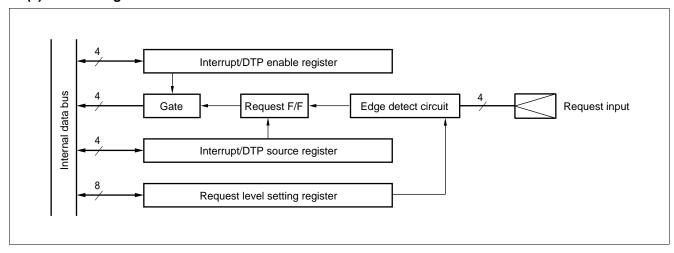

| DTP/external interrupt         |                                                                                                       |                                                                                                               | 8 ir                                                                        | nputs                                                                                        |                                                                                                |                |

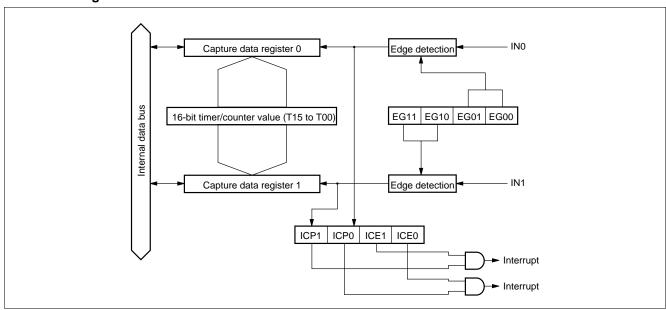

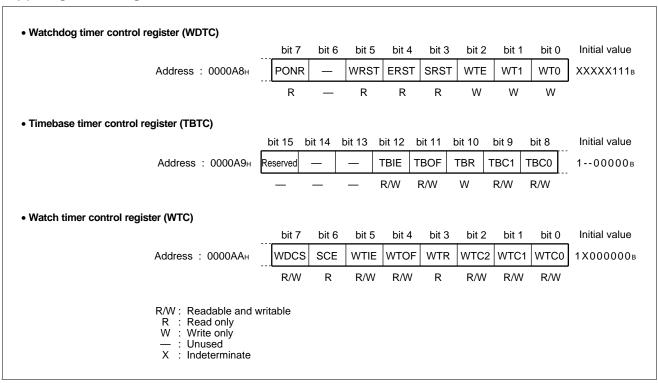

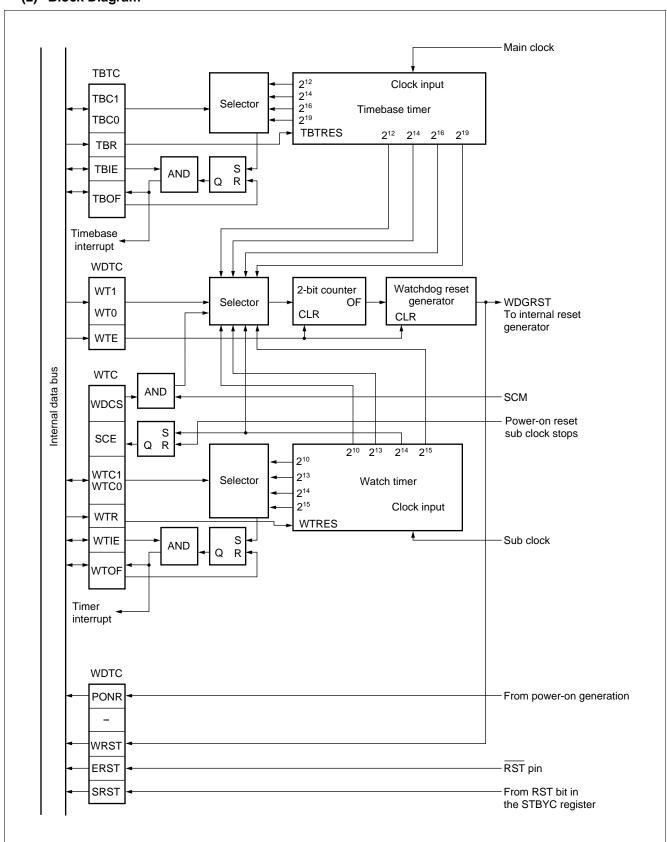

| Timer functions                |                                                                                                       |                                                                                                               | ner (18-bit)/watchdo                                                        | • ' '                                                                                        | , ,                                                                                            |                |

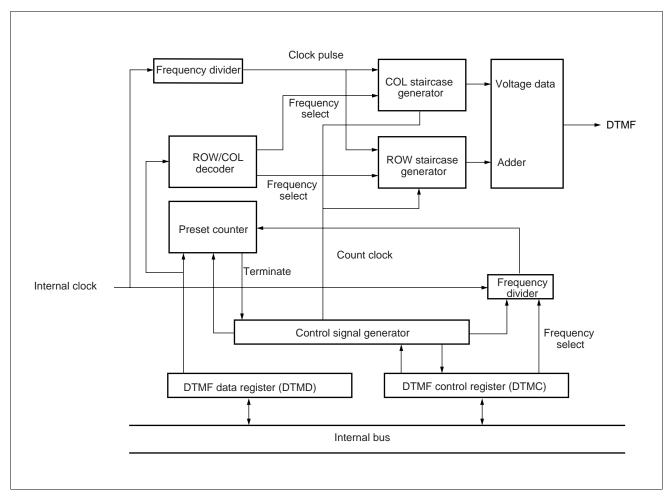

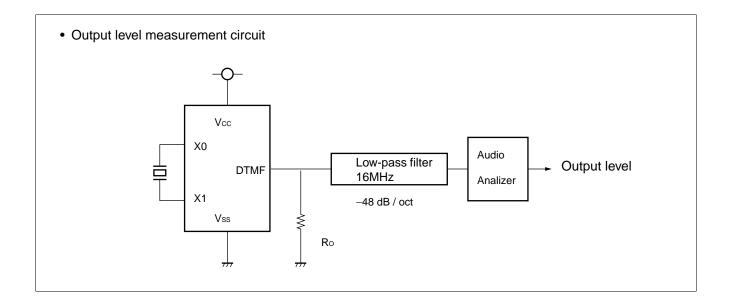

| DTMF generator                 | Supports every ITU-T (CCITT) tone for output (Internal 16 MHz shall be used for DTMF generator).      |                                                                                                               |                                                                             |                                                                                              |                                                                                                |                |

| Low-power consumption modes    | CPU intermittent operation mode, sub clock mode, stop mode, sleep mode, watch mode, pseudo-watch mode |                                                                                                               |                                                                             |                                                                                              |                                                                                                |                |

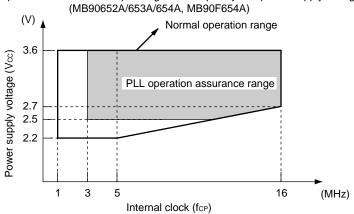

| PLL function                   | (S                                                                                                    | Selectable multiplier: 1/2/3/4 (Set a multiplier that does not exceed the assured operation frequency range.) |                                                                             |                                                                                              |                                                                                                |                |

| Other                          |                                                                                                       |                                                                                                               | V <sub>PP</sub> is shared with<br>the MD2 pin<br>(for EPROM<br>programming) |                                                                                              | _                                                                                              |                |

| Package                        | FPT-                                                                                                  | 100P-M05, FPT-                                                                                                | 100P-M06                                                                    | PGA-256C-A02                                                                                 | FPT-100P-M05                                                                                   | , FPT-100P-M06 |

Notes: • MB90V650A device is assured only when operate with the tools, under the condition of power supply voltage: 2.7 V to 3.3 V, operating temparature: 0°C to 70°C and operating frequency: 1.5 MHz to 8MHz

• For more information about each package, see seciton "PACKAGE DIMENSIONS".

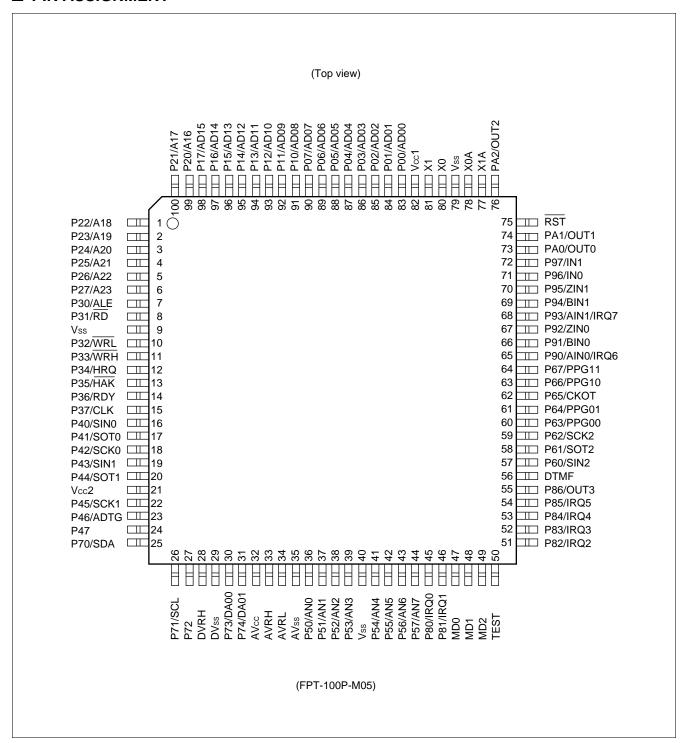

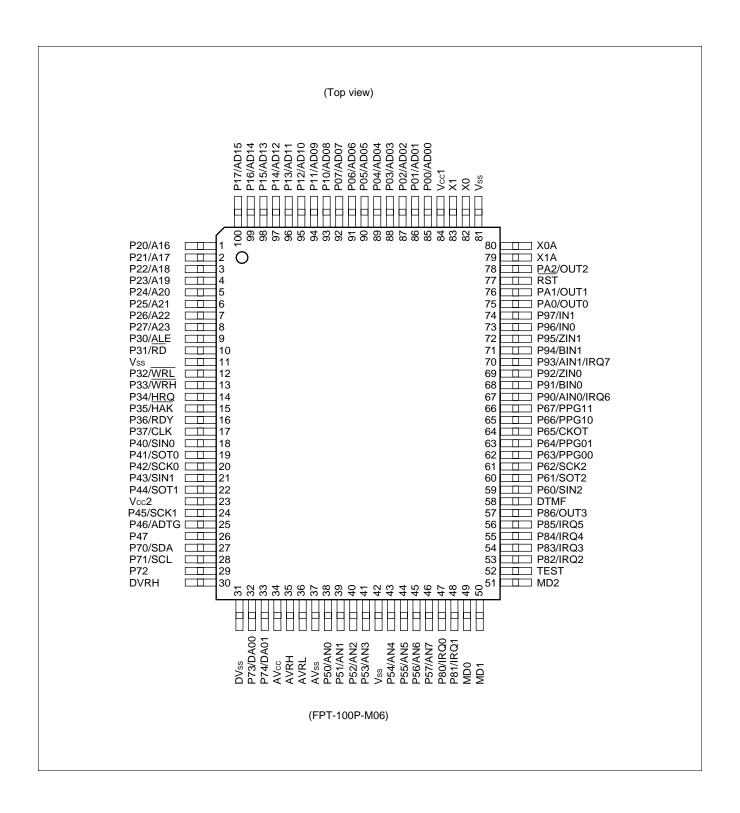

## **■ PIN ASSIGNMENT**

## **■ PIN DESCRIPTION**

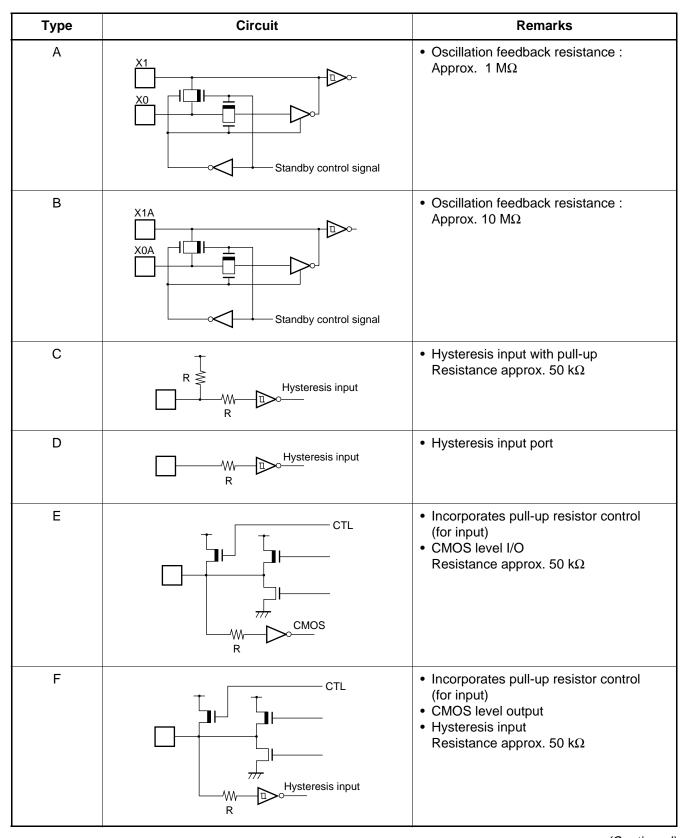

| Pin no.               |                    | D'                         | Circuit     |                                                                                                                                                                                                                                        |  |

|-----------------------|--------------------|----------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP*1                | QFP*2              | Pin name                   | type        | Function                                                                                                                                                                                                                               |  |

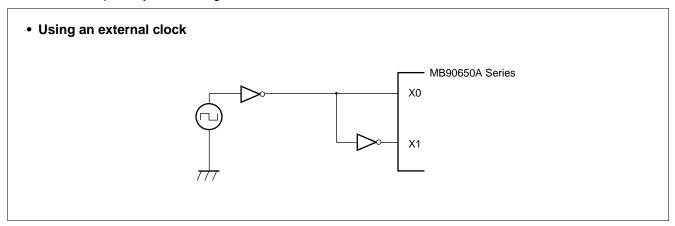

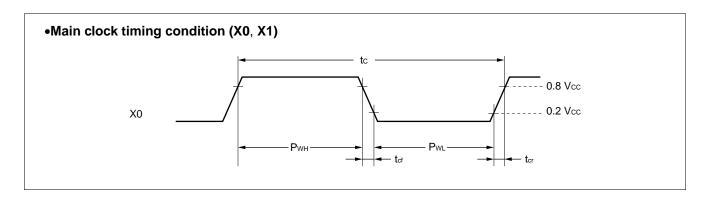

| 80                    | 82                 | X0                         | А           | Crystal oscillator pin                                                                                                                                                                                                                 |  |

| 81                    | 83                 | X1                         | А           | Crystal oscillator pin                                                                                                                                                                                                                 |  |

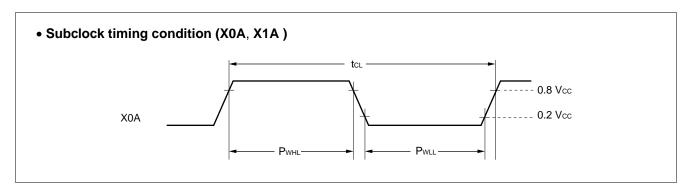

| 77                    | 79                 | X1A                        | В           | Crystal oscillatort pins (32 kHz)                                                                                                                                                                                                      |  |

| 78                    | 80                 | X0A                        | В           | Crystal oscillatort pins (32 kHz)                                                                                                                                                                                                      |  |

| 47 to 49              | 49 to 51           | MD0 to MD2                 | D           | Operating mode selection pins<br>Connect directly to Vcc or Vss.                                                                                                                                                                       |  |

| 50                    | 52                 | TEST                       | D           | Test input pin This pin must always be fixed to "H".                                                                                                                                                                                   |  |

| 75                    | 77                 | RST                        | С           | Reset input pin                                                                                                                                                                                                                        |  |

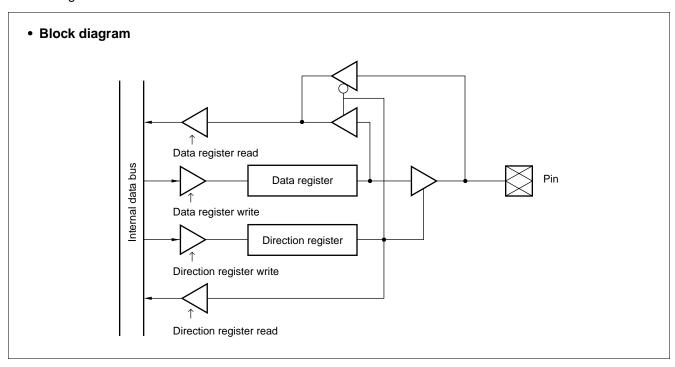

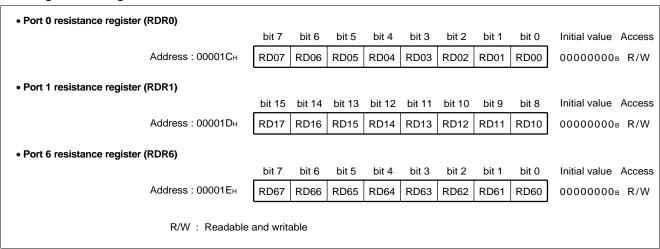

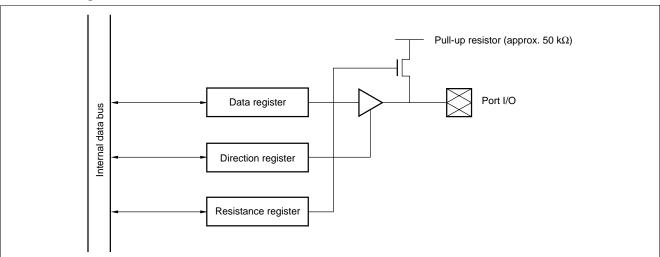

| 83 to 90              | 85 to 92           | P00 to P07                 | E<br>(STBC) | General-purpose I/O ports Pull-up resistors can be set (RD07 to RD00 = "1") using the pull-up resistor setting register (RDR0). The setting does not apply for ports set as outputs (D07 to D00 = "1": invalid at the output setting). |  |

|                       |                    | AD00 to AD07               |             | In external bus mode, the pins function as the lower data I/O or lower address outputs (AD00 to AD07).                                                                                                                                 |  |

| 91 to 98              | 93 to 100          | P10 to P17                 | E<br>(STBC) | General-purpose I/O ports Pull-up resistors can be set (RD17 to RD10 = "1") using the pull-up resistor setting register (RDR1). The setting does not apply for ports set as outputs (D17 to D10 = "1": invalid at the output setting). |  |

|                       |                    | AD08 to AD15               |             | In 16-bit external bus mode, the pins function as the upper data I/O or middle address outputs (AD08 to AD15).                                                                                                                         |  |

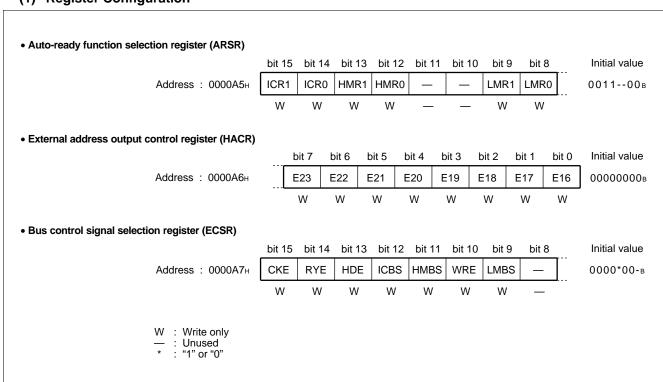

| 99,<br>100,<br>1 to 6 | 1,<br>2,<br>3 to 8 | P20,<br>P21,<br>P22 to P27 | I<br>(STBC) | General-purpose I/O ports In external bus mode, pins for which the corresponding bit in the HACR register is "0" function as the P20 to P27 pins.                                                                                      |  |

|                       |                    | A16,<br>A17,<br>A18 to A23 |             | In external bus mode, pins for which the corresponding bit in<br>the HACR register is "1" function as the upper address output<br>pins (A16 to A23).                                                                                   |  |

| 7                     | 9                  | P30                        | I<br>(STBC) | General-purpose I/O port Functions as the ALE pin in external bus mode.                                                                                                                                                                |  |

|                       |                    | ALE                        |             | Functions as the address latch enable signal.                                                                                                                                                                                          |  |

| 8                     | 10                 | P31                        | I<br>(STBC) | General-purpose I/O port Functions as the RD pin in external bus mode.                                                                                                                                                                 |  |

|                       |                    | RD                         |             | Functions as the read strobe output (RD).                                                                                                                                                                                              |  |

| 10                    | 12                 | P32                        | I<br>(STBC) | General-purpose I/O port Functions as the WRL pin in external bus mode if the WRE bit in the ECSR register is "1".                                                                                                                     |  |

|                       |                    | WRL                        |             | Functions as the lower data write strobe output (WRL).                                                                                                                                                                                 |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

| Pin    | no.                                                                               | D'       | Circuit                                                                                                            | <b>-</b>                                                                                                                                                                                                                                                                                                |  |

|--------|-----------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP*1 | QFP*2                                                                             | Pin name | type                                                                                                               | Function  General-nurpose I/O port                                                                                                                                                                                                                                                                      |  |

| 11     | 13                                                                                | P33      | I<br>(STBC)                                                                                                        | General-purpose I/O port Functions as the WRH pin in 16-bit external bus mode if the WRE bit in the ECSR register is "1".                                                                                                                                                                               |  |

|        |                                                                                   | WRH      |                                                                                                                    | Functions as the upper data write strobe output (WRH).                                                                                                                                                                                                                                                  |  |

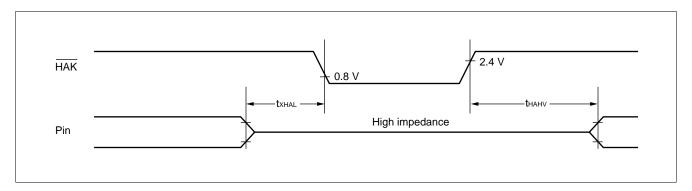

| 12     | 14                                                                                | P34      | I General-purpose I/O port Functions as the HRQ pin in external bus mode if the ECSR register is "1".              |                                                                                                                                                                                                                                                                                                         |  |

|        |                                                                                   | HRQ      |                                                                                                                    | Functions as the hold request input pin (HRQ).                                                                                                                                                                                                                                                          |  |

| 13     | 15                                                                                | P35      | (STBC)                                                                                                             | General-purpose I/O port Functions as the HAK pin in external bus mode if the HDE bit in the ECSR register is "1".                                                                                                                                                                                      |  |

|        |                                                                                   | HAK      |                                                                                                                    | Functions as the hold acknowledge output (HAK) pin.                                                                                                                                                                                                                                                     |  |

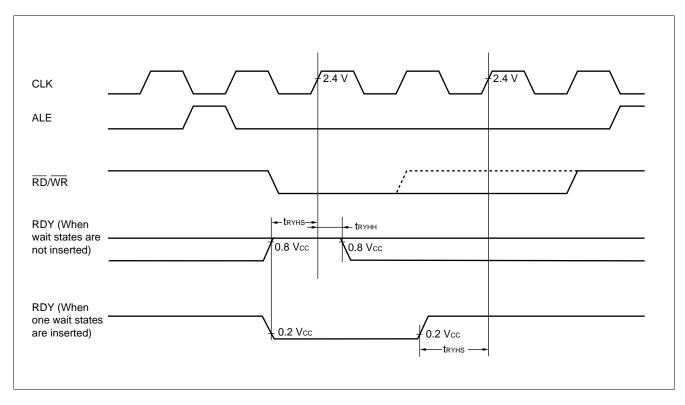

| 14     | 16                                                                                | P36      | I<br>(STBC)                                                                                                        | General-purpose I/O port<br>Functions as the RDY pin in external bus mode if the RYE bit in<br>the ECSR register is "1".                                                                                                                                                                                |  |

|        |                                                                                   | RDY      |                                                                                                                    | Functions as the external ready input (RDY) pin.                                                                                                                                                                                                                                                        |  |

| 15     | 17 P37 I General-purpose I/O port (STBC) Functions as the CLK pin in external bus |          | General-purpose I/O port Functions as the CLK pin in external bus mode if the CKE bit in the ECSR register is "1". |                                                                                                                                                                                                                                                                                                         |  |

|        |                                                                                   | CLK      |                                                                                                                    | Functions as the machine cycle clock output (CLK) pin.                                                                                                                                                                                                                                                  |  |

| 16     | 18                                                                                | P40      | H<br>(STBC)                                                                                                        | General-purpose I/O port When UART0 is operating, the data at the pin is used as the serial input (SIN0). Can be set as an open-drain output port (OD40 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D40 = "0": invalid at the input setting). |  |

|        |                                                                                   | SIN0     |                                                                                                                    | Functions as the UART0 serial input (SIN0).                                                                                                                                                                                                                                                             |  |

| 17     | 19                                                                                | P41      | G<br>(STBC)                                                                                                        | General-purpose I/O port Functions as the SOT0 pin if the SOE bit in the UMC register is "1".  Can be set as an open-drain output port (OD41 = "1") by the open-drain control register (ODR4).  The setting does not apply for ports set as inputs (D41 = "0": invalid at the input setting).           |  |

|        |                                                                                   | SOT0     |                                                                                                                    | Functions as the UART0 serial data output pin (SOT0).                                                                                                                                                                                                                                                   |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

| Pin    | no.   | D:       | Circuit                 | F                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------|-------|----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LQFP*1 | QFP*2 | Pin name | type                    | runction                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

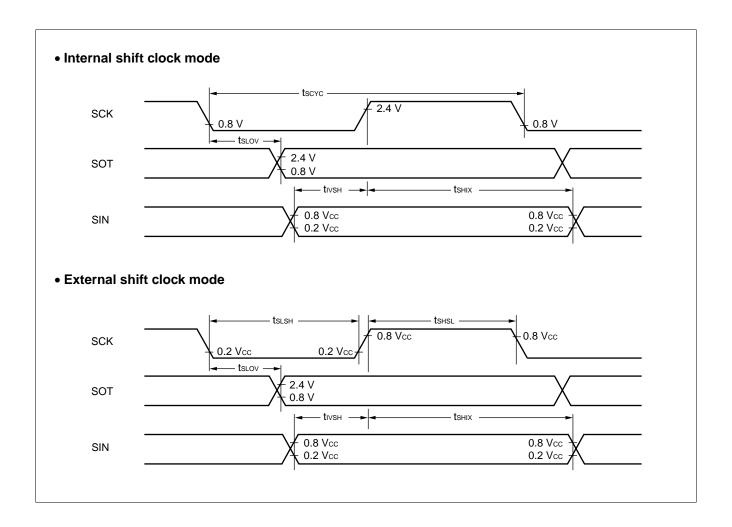

| 18     | 20    | P42      | H<br>(STBC)             | General-purpose I/O port When UART0 is operating in external shift clock mode, the data at the pin is used as the clock input (SCK0). Also, functions as the SCK0 pin if the SOE bit in the UMC register is "1". Can be set as an open-drain output port (OD42 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D42 = "0": invalid at the input setting).                 |  |  |

|        |       | SCK0     |                         | Functions as the UART0 serial clock I/O pin (SCK0).                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 19     | 21    | P43      | H<br>(STBC)             | General-purpose I/O port When I/O extended serial is operating, the data at the pin is used as the serial input (SIN1). Can be set as an open-drain output port (OD43 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D43 = "0": invalid at the input setting).                                                                                                          |  |  |

|        |       | SIN1     |                         | Functions as the serial input for I/O extended serial data.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 20     | 22    | P44 SOT1 | G<br>(STBC)             | General-purpose I/O port Functions as the SOT1 pin if the SOE bit in the UMC register is "1".  Can be set as an open-drain output port (OD44 = "1") by the open-drain control register (ODR4).  The setting does not apply for ports set as inputs (D44 = "0": invalid at the input setting).  Functions as the output pin (SOT1) for I/O extended serial                                                                      |  |  |

|        |       |          |                         | data.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 22     | 24    | P45      | H<br>(STBC)             | General-purpose I/O port When I/O extended serial is operating in external shift clock mode, the data at the pin is used as the clock input (SCK1). Also, functions as the SCK1 pin if the SOE bit in the UMC register is "1".  Can be set as an open-drain output port (OD45 = "1") by the open-drain control register (ODR4).  The setting does not apply for ports set as inputs (D45 = "0": invalid at the input setting). |  |  |

|        |       | SCK1     |                         | Functions as the I/O extended serial clock I/O pin (SCK1).                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 23 25  |       | P46      | G<br>(STBC)             | General-purpose I/O port Can be set as an open-drain output port (OD46 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D46 = "0": invalid at the input setting).                                                                                                                                                                                                         |  |  |

|        |       | ADTG     |                         | Functions as the external trigger input pin for the A/D converter.                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 24     | 26    | P47      | K<br>(NMOS/H)<br>(STBC) | Open-drain type general-purpose I/O port                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

| Section   Percent   Pin name      | Pin    | no.   | Dia nome | Circuit | Function                                                                                                                                                                                                                                                                                                                                                               |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 43 to 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LQFP*1 | QFP*2 | Pin name |         | Function                                                                                                                                                                                                                                                                                                                                                               |  |  |

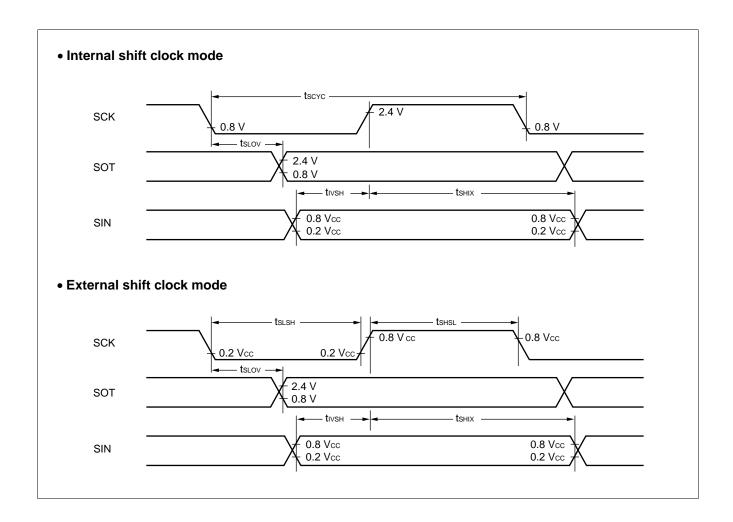

| SIN2  Finctions as a data input pin (SIN2) for I/O extended serial data.  Final does not apply for ports set as outputs (D60 = "1") using the pull-up resistor can be set (RD60 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D60 = "1": invalid at the output setting).  Functions as a data input pin (SIN2) for I/O extended serial.  E (STBC)  Function as the SOT2 pin if the SOE bit in the UMC register is "1".  A pull-up resistor can be set (RD61 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D61 = "1": invalid at the output setting).  Functions as an output pin (SOT2) for I/O extended serial data.  F (STBC)  When I/O extended serial is operating in external shift clock mode, the data at the pin is used as the clock input (SCK2). A pull-up resistor can be set (RD62 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D62 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D62 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D63 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D63 = "1") invalid at the output setting).  Functions as the I/O extended serial clock I/O pin (SCK2). General-purpose I/O port A pull-up resistor can be set (RD63 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D63 = "1") invalid at the output setting).  Functions as the PPG00 output when PPG output is enabled.  E (STBC) Functions as the PPG00 output when PPG output is enabled.  General-purpose I/O port A pull-up resistor can be set (RD64 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D64 = "1") invalid at the output setting).                         |        |       |          | _       | General-purpose I/O ports                                                                                                                                                                                                                                                                                                                                              |  |  |

| STBC    A pull-up resistor can be set (RD60 = "1") using the pull-up resistor setting register (RDR6).   SIN2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |       |          |         |                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Solution   February   Function    | 57     | 59    | P60      |         | A pull-up resistor can be set (RD60 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D60 = "1":                                                                                                                                                                                                        |  |  |

| STBC    Function as the SOT2 pin if the SOE bit in the UMC register is "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |       | SIN2     |         | Functions as a data input pin (SIN2) for I/O extended serial.                                                                                                                                                                                                                                                                                                          |  |  |

| F (STBC)  F (STB | 58     | 60    | P61      |         | Function as the SOT2 pin if the SOE bit in the UMC register is "1".  A pull-up resistor can be set (RD61 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D61 = "1":                                                                                                                                   |  |  |

| (STBC)  When I/O extended serial is operating in external shift clock mode, the data at the pin is used as the clock input (SCK2). Also, functions as the SCK2 pin if the SOE bit in the UMC register is "1".  A pull-up resistor can be set (RD62 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D62 = "1": invalid at the output setting).  SCK2  Functions as the I/O extended serial clock I/O pin (SCK2).  General-purpose I/O port A pull-up resistor can be set (RD63 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D63 = "1": invalid at the output setting).  PPG00  Functions as the PPG00 output when PPG output is enabled.  General-purpose I/O port A pull-up resistor can be set (RD64 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D64 = "1": invalid at the output setting).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |       | SOT2     |         | Functions as an output pin (SOT2) for I/O extended serial data.                                                                                                                                                                                                                                                                                                        |  |  |

| 60 62 P63 E (STBC) General-purpose I/O port A pull-up resistor can be set (RD63 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D63 = "1": invalid at the output setting).  Functions as the PPG00 output when PPG output is enabled.  61 63 P64 E (STBC) General-purpose I/O port A pull-up resistor can be set (RD64 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D64 = "1": invalid at the output setting).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59     | 61    | P62      |         | When I/O extended serial is operating in external shift clock mode, the data at the pin is used as the clock input (SCK2). Also, functions as the SCK2 pin if the SOE bit in the UMC register is "1".  A pull-up resistor can be set (RD62 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D62 = "1": |  |  |

| (STBC)  A pull-up resistor can be set (RD63 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D63 = "1": invalid at the output setting).  Functions as the PPG00 output when PPG output is enabled.  E (STBC)  General-purpose I/O port A pull-up resistor can be set (RD64 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D64 = "1": invalid at the output setting).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |       | SCK2     |         | Functions as the I/O extended serial clock I/O pin (SCK2).                                                                                                                                                                                                                                                                                                             |  |  |

| 61 63 P64 E (STBC) General-purpose I/O port A pull-up resistor can be set (RD64 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D64 = "1": invalid at the output setting).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60     | 62    | P63      |         | A pull-up resistor can be set (RD63 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D63 = "1":                                                                                                                                                                                                        |  |  |

| (STBC) A pull-up resistor can be set (RD64 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D64 = "1": invalid at the output setting).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |       | PPG00    |         | Functions as the PPG00 output when PPG output is enabled.                                                                                                                                                                                                                                                                                                              |  |  |

| PPG01 Functions as the PPG01 output when PPG output is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61     | 63    | P64      |         | A pull-up resistor can be set (RD64 = "1") using the pull-up resistor setting register (RDR6).  The setting does not apply for ports set as outputs (D64 = "1":                                                                                                                                                                                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |       | PPG01    |         | Functions as the PPG01 output when PPG output is enabled.                                                                                                                                                                                                                                                                                                              |  |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

| Pin    | no.   |          | Circuit                                                                                                                                                                                                         |                                                                                                                                                                                                                         |  |

|--------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP*1 | QFP*2 | Pin name | type                                                                                                                                                                                                            | Function                                                                                                                                                                                                                |  |

| 62     | 64    | P65      | E (STBC) General-purpose I/O port A pull-up resistor can be set (RD65 = "1") using the presistor setting register (RDR6). The setting does not apply for ports set as outputs (Dinvalid at the output setting). |                                                                                                                                                                                                                         |  |

|        |       | СКОТ     |                                                                                                                                                                                                                 | Functions as the CKOT output when CKOT is operating.                                                                                                                                                                    |  |

| 63     | 65    | P66      | E<br>(STBC)                                                                                                                                                                                                     | General-purpose I/O port A pull-up resistor can be set (RD66 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D66 = "1": invalid at the output setting). |  |

|        |       | PPG10    |                                                                                                                                                                                                                 | Functions as the PPG10 output when PPG output is enabled.                                                                                                                                                               |  |

| 64     | 66    | P67      | E<br>(STBC)                                                                                                                                                                                                     | General-purpose I/O port A pull-up resistor can be set (RD67 = "1") using the pull-up resistor setting register (RDR6). The setting does not apply for ports set as outputs (D67 = "1": invalid at the output setting). |  |

|        |       | PPG11    |                                                                                                                                                                                                                 | Functions as the PPG11 output when PPG output is enabled.                                                                                                                                                               |  |

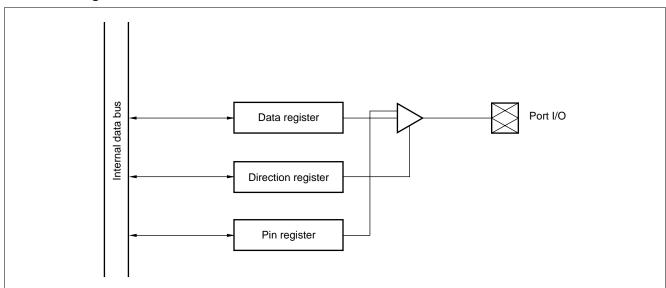

| 25     | 27    | P70      | K                                                                                                                                                                                                               | Open-drain type I/O port                                                                                                                                                                                                |  |

|        |       | SDA      | (NMOS/H)<br>(STBC)                                                                                                                                                                                              | I <sup>2</sup> C interface data I/O pin This function is valid when I <sup>2</sup> C interface operations are enabled. Set port output to Hi-Z (PDR = 1) during I <sup>2</sup> C interface operations.                  |  |

| 26     | 28    | P71      | K                                                                                                                                                                                                               | Open-drain type I/O port                                                                                                                                                                                                |  |

|        |       | SCL      | (STBC)                                                                                                                                                                                                          | I <sup>2</sup> C interface clock I/O pin This function is valid when I <sup>2</sup> C interface operations are enabled. Set port output to Hi-Z (PDR = 1) during I <sup>2</sup> C interface operations.                 |  |

| 27     | 29    | P72      | K<br>(STBC)                                                                                                                                                                                                     | Open-drain type I/O port                                                                                                                                                                                                |  |

| 30     | 32    | P73      | M<br>(STBC)                                                                                                                                                                                                     | Open-drain type I/O port<br>Functions as a D/A output pin when DAE0 = "1" in the D/A<br>control register (DACR).                                                                                                        |  |

|        |       | DA00     |                                                                                                                                                                                                                 | Functions as D/A output 0 when the D/A converter is operating.                                                                                                                                                          |  |

| 31     | 33    | P74      | M<br>(STBC)                                                                                                                                                                                                     | General-purpose I/O port Functions as a D/A output pin when DAE1 = "1" in the D/A control register (DACR).                                                                                                              |  |

|        |       | DA01     |                                                                                                                                                                                                                 | Functions as D/A output 1 when the D/A converter is operating.                                                                                                                                                          |  |

| 45     | 47    | P80      | J                                                                                                                                                                                                               | General-purpose I/O port                                                                                                                                                                                                |  |

|        |       | IRQ0     |                                                                                                                                                                                                                 | Functions as external interrupt request I/O 0.                                                                                                                                                                          |  |